コンピュータシステム - 3.コンピュータ構成要素 - 2.メモリ - 4.アクセス方式

「メモリインタリーブ」とは、主記憶装置を複数の独立した部分(バンク)に分けて、各バンクに連続的にアクセスすることで、「サイクル時間」の短縮を図った技術。この方式では、キュッシュメモリへのデータ転送やバイブライン制御でのデータの先読みなどに効果的です。アドレスは各バンクを横断するように割り付ける。

メモリの読み書きにはいくつかの段階があり、CPUがアクセス要求を行なってから実際にデータが送られてくる(あるいは書き込みが完了する)までは次のデータの読み書きができない。このレイテンシ(遅延)と呼ばれる時間差が生じる。

メモリへのアクセスは時間がかかるため、コンピュータの処理速度はこの「待ち時間」に足を引っ張られている。レイテンシを短縮する試みは常に行なわれているが、CPU内の記憶素子との差は埋めがたく、また、低レイテンシのメモリは高価である。

一方、メモリへのアクセス要求は短期的には局所性が極めて強く、連続した領域に順番に読み書きを行なうことが多い。この特徴を利用して、複数のメモリバンクにまたがって連続したアドレスを交互に振っておき、あるデータにアクセスする遅延時間の最中に次のアドレスへアクセス要求を発行して時間を有効利用するのがメモリインターリーブである。

バンクの数を増やせばその分高速にアクセスできるようになり、2つのバンクを用意すれば2倍、4つで4倍の高速化を図ることができる。ただし、実際にはコントローラのオーバーヘッドや、不連続なアドレスへのアクセスがあるため、バンクの数だけ性能が向上するわけではない。

安価な高レイテンシのメモリで高い性能を得られる反面、メモリコントローラが複雑になり高価になることや、部品点数が増えて故障率が上がってしまうという欠点もある。高い性能が要求されるサーバなどでよく使われる技術だが、最近ではパソコンでもメモリインターリーブが採用されていることがあり、メモリの増設の際に同じ容量・種類のメモリモジュールを2枚ずつ増設しなければならないことがある

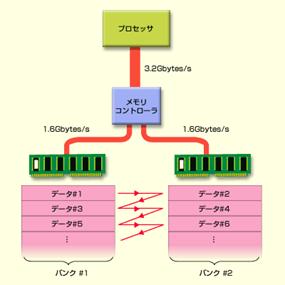

【 メモリ・インターリーブの仕組み 】

これは1.6Gbytes/sの帯域幅を持つ2つのメモリ・バンクを例としている。各メモリ・バンクに対しては、連続したアドレスを交互に割り振っておく。例えばプロセッサがデータ#1、#2、#3… という具合に連続してアクセスする場合、メモリ・コントローラは2つのバンクに対してほぼ同時にアクセスすることで、通常時(1.6Gbytes/s)の約2倍の性能(約3.2Gbytes/s)が得られる。

あるアドレスのメモリへアクセスを実行すると、まずはアドレスから該当するメモリチップを選択する信号が生成され、選択信号を入力されたメモリチップはアクティブになり、読み書き可能な状態になる。 そして読み出し(Read Cycle)もしくは書き込み(Write Cycle)の信号を受けて該当の処理をする。ここまでの間には、多少なり時間が消費されている。これを連続して同じチップをアクセスしないようにし、たとえば奇数・偶数アドレスでメモリモジュールを分けたバンク構成にし、奇数アドレスのメモリチップに選択信号を送り、Read/Writeを実行している間に平行して偶数アドレスのメモリチップに選択信号を送る。 そうすると、CPUが次のメモリアクセスを要求したときに既にアクティブになっているのでチップ選択の遅延が軽減される。

- 平成23年度春期 問12 メモリインタリーブ

- 平成21年度秋期 問10 メモリインタリーブ

- 平成20年度秋期 問20 メモリインタリーブ

- 平成19年度秋期 問22 メモリインタリーブ

- 平成13年度春期 問22 メモリインタリーブ

- 平成13年度秋期 問23 メモリインタリーブ

www.it-shikaku.jp