コンピュータシステム - 3.コンピュータ構成要素 - 1.プロセッサ - 6.プロセッサの動作原理

1 演算の仕組み

|

【 AND 回路 】 A が 1 かつ B が 1 のときのみ 出力 Y が 1 になる回路 |

【 NAND 回路 】 A が 1 かつ B が 1 のときのみ 出力 Y が 0 になる回路 | |||||||||||||||||||||||||||||||||

|

|

|

|

|||||||||||||||||||||||||||||||

|

【 OR 回路 】 A が 1 または B が 1 のとき 出力 Y が 1 になる回路 |

【 NOR 回路 】 A が 1 または B が 1 のとき 出力 Y が 0 になる回路 | |||||||||||||||||||||||||||||||||

|

|

|

|

|||||||||||||||||||||||||||||||

|

【 NOT 回路 】 A が 1 のとき出力 Y は 0、A が 0 のとき 出力 Y は 1 になる回路 |

【 XOR 回路 】 A と B が 異なる時 出力 Y が 1 になる回路 | ||||||||||||||||||||||||

|

|

|

|

||||||||||||||||||||||

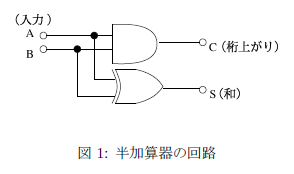

下位の桁からの桁上がり(キャリー)を考慮しないもの。

特徴としては、「桁の値(S)」は「排他的論理和」となり、「桁上がり(C)」は「AND」となる。

|

|

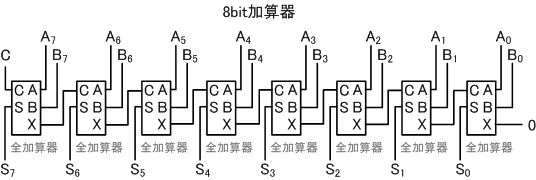

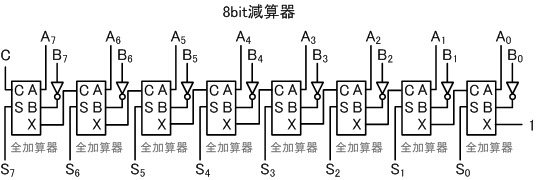

下位の桁からの桁上がりを考慮するもの。この場合は。下位の桁からの桁上がりを考慮するため、入力は3つとなる。

|

|

【 順序回路 】

「外部入力と回路自体の状態によって出力が決まる」というもの。

内部に状態を持つ回路であり、外部からの入力だけでは一義的に出力は決まらない。

入力と内部状態の両方の値により、その出力が定まる論理回路。

代表的なものに「フリップフロップ回路」がある。これは「記憶装置(メモリ)」で利用されている。

Qの出力を保持するのに使われる。

- Q に 1 をセットするには、 S に 1 を入力。

- Q に 1 が出力されたら、S を 0 に戻しても Q の 1 は変わらない。

- Q を 0 に戻すには、S が 0 の状態で R に 1 を入力すると Q は 0 に戻る。

- Q が 0 の状態で R を 0 に戻しても Q は 0 のまま変わらない。

|

|

|||||||||||||||||||||||

フリップフロップ回路(wmv) (クリックするとダウンロードされます。そのファイルを実行してください。)

【 組み合わせ回路 】

論理回路の内部の状態とは関係なく、出力がその時点における入力の値の組合せにより定まる論理回路のこと。

2 命令とアドレッシング

「命令部」は「実行する操作」で CPU が処理するための命令の種類を表す。

「オペランド部(アドレス部)」は「操作の対象となるデータのアドレスやレジスタ」もしくは「データの値そのもの」を示す。

- 0 アドレス方式

後入れ先出しのスタック(LIFO)で使用します。処理対象のデータがスタックに格納されているコンピュータで使用される。例えば、加算や乗算などの演算は、スタックの上二つを取り出して演算結果をスタックにプッシュする。よって、命令語は、ADD, MULのように一語で表現できる。

- 1 アドレス方式

主に「アキュームレータ」へある番地の内容を足し込む場合に使用します。加算や乗算の対象となる二つのデータのうち、少なくとも一方がレジスタ上に存在しなくてはならない命令形式。たとえば、「ADD レジスタA メモリX」(レジスタAの中身とメモリXの中身の和をレジスタAに保存せよ)という命令は書けても、「ADD メモリX メモリY」などとは書けない。演算対象にしたいデータは、一旦、レジスタにロードする必要がある。

- 2 アドレス方式

これは、A番地とB番地の内容を加算してA番地へ書き込むような場合に使用します。演算対象の二つの数値が共にメモリに存在していても、演算できる方式。例えば、「ADD メモリX メモリY」(メモリXの中身とメモリYの中身の和をメモリXに保存せよ)という命令が使える。

- 3 アドレス方式

A番地とB番地の内容を加算してC番地へ書き込むような場合に使用します。2アドレス命令形式に対し、データの保存場所を指定できるようにしたもの。例えば、「ADD メモリX メモリY メモリZ」(メモリYの中身とメモリZの中身の和をメモリXに保存せよ)という命令が使える。

コンピュータが命令を実行する場合、以下の手順を行う。

- 命令レジスタに命令を取出す(命令フェッチ)

- 命令デコーダで命令の解読(デコード)

- アドレスの計算

- オペランドの取り出し

- 演算の実行

- 演算結果の格納

命令サイクルとは、「CPUが主記憶装置から一つの命令を取り出してから、その命令の実行を終了するまでの過程」のこと

- 即値アドレス指定方式

オペランド部にアドレスではなく、操作対象となるデータが入っている方式。

レジスタの初期化やアドレスを計算するような場合で使われる。

- 直接アドレス指定方式

オペランド部に、操作対象のデータが入っているメインメモリのアドレスが指定されている方式。

- 間接アドレス指定方式

オペランド部に指定されているアドレスを、操作対象のデータが格納されているメインメモリのアドレスとする方式。

- インデックスアドレス指定方式(指標アドレス指定方式)

オペランド部の内容とインデックスレジスタの内容を加算したものを有効アドレスとする方式。指標アドレス方式とも言います。この方法は、配列などの主記憶上の連続した繰り返し処理に適しています。

- ベースアドレス指定方式

オペランド部とベースレジスタの内容の和を操作対象のデータが入っているメインメモリのアドレスとする方式。

リロケータブルなプログラムで利用される。

- 相対アドレス指定方式

オペランド部とプログラムカウンタの和を操作対象のデータが入っているメインメモリのアドレスとする方式。

相対アドレス指定方式は、リロケータブルなプログラム(メモリの任意の場所にプログラムを置くことができるプログラムのこと)を作成する際に用いられます。

- レジスタアドレス方式

オペランド部に汎用レジスタの番号を指定し、そのレジスタに格納されている内容をアドレスと指定する、または操作対象のデータとする方式。

【 算術演算命令 】

整数データに対して四則演算を行う。

算術加算:ADDA

算術減算:SUBA

【 論理演算命令 】

論理演算を行う。論理積・論理和・排他的論理和・否定等がある。

論理積:AND

論理和:OR

排他的論理和:XOR

【 比較命令 】

レジスタの内容と主記憶装置の内容との大小比較を行います。結果を「フラグレジスタ」へセットする。

算術比較:CPA

論理演算:CPL

【 分岐命令 】

プログラムカウントに任意の値を設定することにより、次に実行する命令を元の順番とは別のアドレスにある命令とすること。

判断条件によって次に実行する命令を決める「条件分岐命令」と無条件で次に実行する命令に分岐する「無条件分岐命令」がある。

正分岐:JPL

負分岐:JMI

無条件分岐:JUMP

【 シフト命令 】

レジスタの内容を指定したビット数分だけシフトさせる命令です。以下の種類がある。

| シフト命令 | 内容 |

| 論理左シフト | 3 ビットシフトさせる場合、左 3 桁は捨てられ、右に「 0 」を補う |

| 論理右シフト | 3 ビットシフトさせる場合、右 3 桁は捨てられ、左に「 0 」を補う |

| 算術左シフト | 3 ビットシフトさせる場合、最上位ビットはシフトせず、それ以降の 3 ビットは捨てられ、右に「 0 」を補う。 |

| 算術右シフト | 3 ビットシフトさせる場合、右 3 桁は捨てられ、左は、最上位ビットはシフトせず、その他は、最上位ビットの値を補う。 |

| 回転シフト | シフトを巡回していくような方法で行うもの。例を以下に示す。 ・10110 右へ 3 ビット回転シフトすると、01101 ・10110 を左へ 3 ビット回転シフトすると、 10101 |

「左シフト」の場合は、n ビットのシフトで、2n 倍になる。

「右シフト」の場合は、n ビットのシフトで、2-n 倍になる。

算術左シフト:SLA

算術右シフト:SRA

論理左シフト:SLL

論理右シフト:SRL

【 転送命令 】

レジスタ間や主記憶装置間・レジスタと主記憶装置間でデータ転送を行う。

ロード:LD

ストア:ST

【 入出力命令 】

入出力装置と主記憶装置間でデータの転送を行う。

3 割込み

プログラムの実行途中で強制的に処理を中断し、別のプログラムを実行する仕組みを割り込みという。

【 割り込みの手順 】

- 割り込み原因が発生

- 割り込みを検知する

- 現在処理中のプログラムカウンタの値を退避する。(次の命令)

- 割り込んだプログラムの先頭アドレスをプログラムカウンタにセットする

- 今まで処理していたレジスタの内容を退避する

- 割り込んだプログラムを実行する

- 割り込みプログラムが終了

- 退避していた命令アドレスをプログラムカウンタにセットする

- 退避していたレジスタの内容を元のレジスタに戻す

- 前のプログラムを割り込み時点から実行する

プログラムの理由による割り込み

- プログラム割り込み(3)・・・プログラムの実行中に異常が発生した場合(オーバーフロー・ゼロ除算など)の割込み。プログラムの誤り

- ページフォルト割り込み(3)・・・メモリ上に存在しないページにアクセスしたときに起こる割り込み。

- SVC(スーパーバイザコール)割り込み(システムコール)(4) ・・・プログラムからOSに入出力の依頼があった時に生じる割込み。

- 記憶保護例外割り込み(3)・・・書込み保護されている記憶領域を書き換えしようとしたため起こる割込み。

プログラム以外の原因で生じる割込み

- マシンチェック割込み(1)・・・ハードウェアの異常・誤動作、メモリ障害、電源異常などが生じた時の割込み。

- コンソール割込み(2)・・・オペレータが介入する時の割込み。

- タイマ割込み(2)・・・監視タイマでCPU使用時間を経過した時に生じる割込み。プログラムの処理を切り替えるときのタイミングになる。

- 入出力割込み(5)・・・周辺機器の入出力処理の終了や誤動作が生じた時の割込み。

※ ()内数字は優先度を表す。

- 平成30年度春期 問10 内部割込み

- 平成29年度春期 問22 半加算器

- 平成29年度秋期 問10 割込み 外部割込み

- 平成29年度秋期 問23 論理回路

- 平成28年度秋期 問09 アドレス指定方式

- 平成27年度春期 問23 論理回路

- 平成26年度春期 問22 論理回路

- 平成26年度秋期 問10 内部割込み

- 平成26年度秋期 問21 論理回路

- 平成25年度春期 問10 アドレス指定方式

www.it-shikaku.jp